利用缝隙抑制型钨填充接触区工艺来降低良率损失

2016年07月21日 9:9 16179次浏览 来源: OFweek 电子工程网 分类: 钨

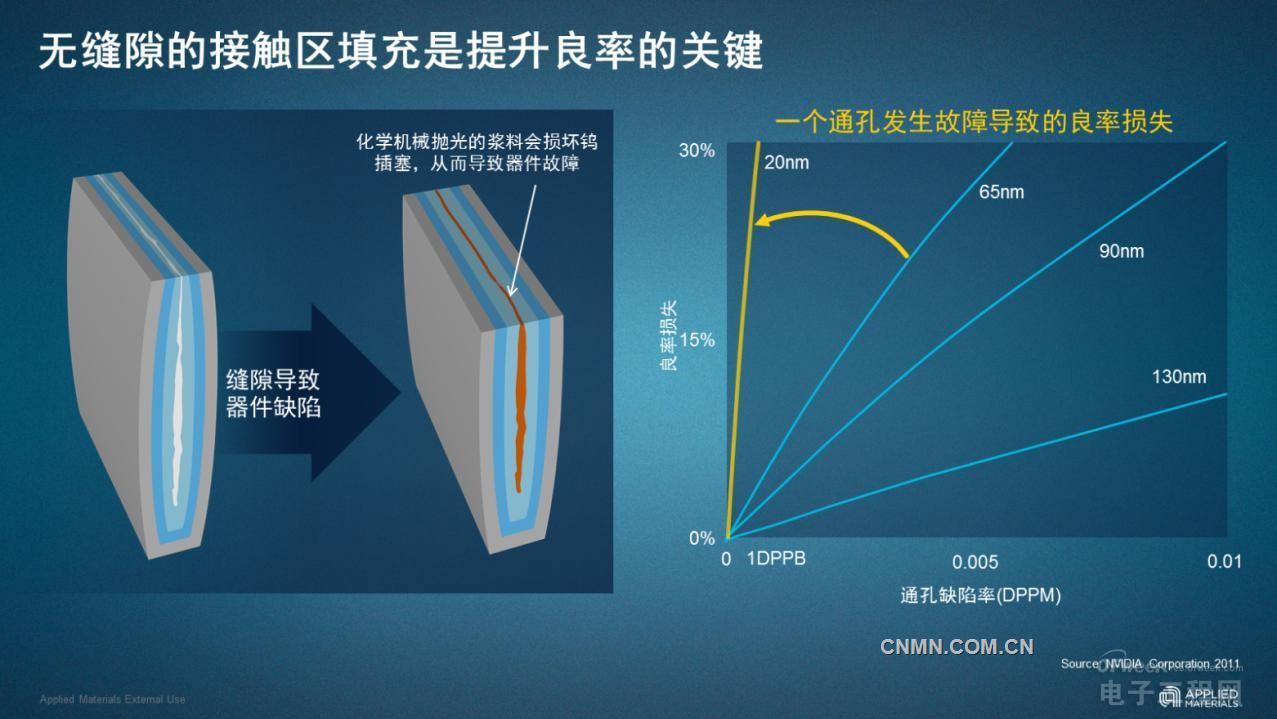

我们的新方法采用了独特的“选择性”抑制机制,可生成自下而上的填充,而不会产生缝隙和孔洞问题。对成核层的上部区域进行特殊的预处理可促成钨自下而上生长,从而尽可能减少因夹断而造成的孔洞或接触区缝隙的产生。

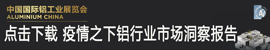

在早先的技术节点中,由于器件尺寸较大,能采用成核及平整化化学气相沉积(CVD)技术进行钨(W)填充。如今,由于插塞处的超小开口很容易发生悬垂现象,因此薄膜表面均匀生长的共形阶段可能在填充完成前就关闭或夹断,从而留下孔洞。即使没有孔洞,由于填充物从侧壁生长,在共形沉积时必然会在中间形成中心缝隙问题。

这些属性使极细小的成核层在化学机械抛光(CMP)过程中容易被渗透,使CMP浆料进入,从而破坏钨插塞。这会导致高电阻产生,或使得负责传递晶体管信号的互连完全损坏。先进芯片设计中的高密度特征以及缺乏多余的通孔,意味着一个简单的孔洞就会造成器件完全损坏,从而带来严重的良率损失(图1)。

利用缝隙抑制型钨填充接触区工艺来降低良率损失

图1

上图中,y轴显示了器件的良率损失,x轴为通孔缺陷率。十亿分之一的缺陷就会导致20nm节点的芯片产生15%以上的良率损失,而在更小节点的器件中这一情况会更为严重。

我们的新方法采用了独特的“选择性”抑制机制,可生成自下而上的填充,而不会产生缝隙和孔洞问题。对成核层的上部区域进行特殊的预处理可促成钨自下而上生长,从而尽可能减少因夹断而造成的孔洞或接触区缝隙的产生。

这一“缝隙抑制型钨填充工艺”(SSW)有效优化了钨的体积,可制成更牢固的成核表面,便于填充后续的集成工序。这样也可以降低对CMP和介质蚀刻工艺的要求,从而带来性能、产品设计和良率方面的改善。

利用缝隙抑制型钨填充接触区工艺来降低良率损失

作者: 应用材料公司金属沉积产品事业部 接触和中段产品线全球经理Jonathan Bakke

责任编辑:周大伟

如需了解更多信息,请登录中国有色网:www.yujingqiu.com了解更多信息。

中国有色网声明:本网所有内容的版权均属于作者或页面内声明的版权人。

凡注明文章来源为“中国有色金属报”或 “中国有色网”的文章,均为中国有色网原创或者是合作机构授权同意发布的文章。

如需转载,转载方必须与中国有色网( 邮件:cnmn@cnmn.com.cn 或 电话:010-63971479)联系,签署授权协议,取得转载授权;

凡本网注明“来源:“XXX(非中国有色网或非中国有色金属报)”的文章,均转载自其它媒体,转载目的在于传递更多信息,并不构成投资建议,仅供读者参考。

若据本文章操作,所有后果读者自负,中国有色网概不负任何责任。